[Jain, 2(6): June, 2015] ISSN 2349-6193 Impact Factor (PIF): 2.243

# International Journal OF Engineering Sciences & Management Research

# A SURVEY ON DESIGN AN EFFICIENT ARCHITECTURE FOR HIGH SPEED CONVOLUTION AND DECONVOLUTION PROCESS

### Ms. Priya R.Jain\*, Prof. Dr.Ujwalla A.Bellorkar

\*PG Student ,ENTC Department ,HVPM'S College of Engineering and Technology, Amravati ,India Head & Asst. Professor, ENTC Department ,HVPM'S College of Engineering and Technology, Amravati ,India

**Keywords:** Linear Convolution, Deconvolution, Radix-2 Booth Multiplier, Radix-4 Booth Multiplier, Urdhav Tiryagbhyam, Digital signal processing.

### **ABSTRACT**

In Digital Signal Processing, the convolution and deconvolution with a very long sequence is ubiquitous in many application areas. They consume much of time. This paper presents a direct method of computing the discrete linear convolution, circular convolution and deconvolution. The most significant aspect, is the development of a multiplier and divider architecture based on high speed algorithm. It shows that the implementation of linear convolution and circular convolution is efficient in terms of area and speed compared to their implementation using conventional multiplier & divider architectures. In this paper we study different forms of high speed convolution and deconvolution system using FPGA.

#### INTRODUCTION

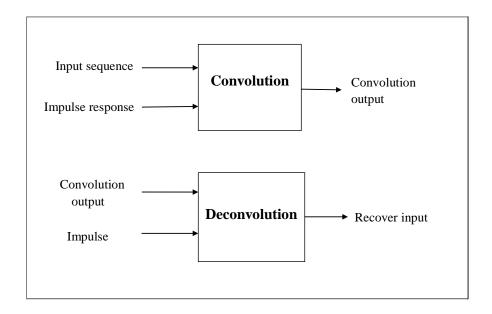

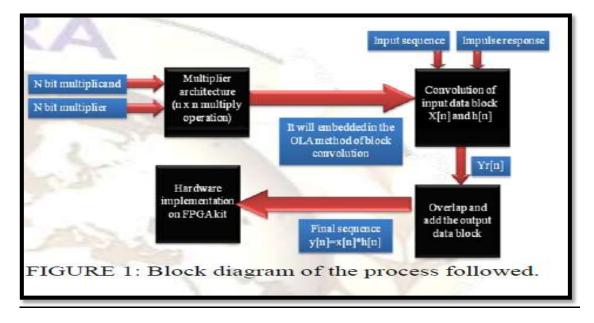

Convolution and deconvolution is the most important and fundamental concept in signal processing and analysis. However, beginners often struggle with convolution and decovolution because the concept and computation requires a number of steps that are tedious and slow to perform. Therefore many of researchers have been trying to improve performance parameters of convolution and deconvolution system using new algorithms and hardware. Complexity and excess time consumption are always the major concern of engineers which motivates them to focus on more advance and simpler techniques. Pierre and John have implemented a fast method for computing linear convolution, circular convolution and deconvolution. This method is similar to the multiplication of two decimal numbers and this similarity makes this method easy to learn and quick to compute. Also to compute deconvolution of two finite length sequences, a novel method is used. This method is similar to computing long-hand division and polynomial division .Following diagram shows the overall process of high speed convolution and deconvolution process. With the latest advancement of VLSI technology, digital signal processing plays a pivotal role in many areas of electrical engineering, of Digital Signal Processing and Image Processing. It is used for designing of digital filter and correlation application. However, beginners often struggle with convolution because the concept and computation requires a number of steps that are tedious and slow to perform. Discrete convolution is central to many applications. The most commonly taught approach is a graphical method because of the visual insight into the convolution mechanism. Graphical convolution is very systematic to compute but is also very tedious and time consuming. The principal components required for implementation of convolution calculation are adder and multiplier for partial multiplication. Therefore the partial multiplication and addition are bottleneck in deciding the overall speed of the convolution implementation technique. Complexity and excess time consumption are always the major concern of engineers which motivates them to focus on more advance and simpler techniques.

[Jain, 2(6): June, 2015]

### International Journal OF Engineering Sciences & Management Research

Fig 1.Block diagram of Convolution and Deconvolution process

#### LITERATURE REVIEW

Surabhi Jain & Sandeep Saini [1] presents a direct method of computing the discrete linear convolution, circular convolution and deconvolution. The approach is easy to learn because of the similarities to computing the multiplication of two numbers. The most significant aspect of the proposed method is the development of a multiplier and divider architecture based on Ancient Indian Vedic Mathematics sutras Urdhvatriyagbhyam and Nikhilam algorithm. The results show that the implementation of linear convolution and circular convolution using vedic mathematics is efficient in terms of area and speed compared to their implementation using conventional multiplier & divider architectures.

G.Ramanjaneya Reddy, A. Srinivasulu [2] presents an on the spot methodology of reducing convolution processing time using hardware computing and implementations of discrete linear convolution of two finite length sequences (NXN). This implementation method is realized by simplifying the convolution building blocks. The purpose of this analysis is to prove the feasibility of an FPGAthat performs a convolution on an acquired image in real time. In addition, the presented circuit uses less power consumption and delay from input to output. It additionally provides the required modularity, expandability, and regularity to form different convolutions for any variety of bits.-+.

Sukhmeet Kaur, Suman and Manpreet Signh Manna [3] describes implementation of radix-4 Modified Booth Multiplier and this implementation is compared with Radix-2 Booth Multiplier. Modified Booth's algorithm employs both addition and subtraction and also treats positive and negative operands uniformly .No special actions are required for negative numbers. The Speed and Circuit Complexity is compared, Radix-4 Booth Multiplier is giving higher speed as compared to Radix-2 Booth Multiplier and Circuit Complexity is also less as compared to it.

Madhura Tilak [4] presents a novel method of implementing linear convolution of two proposed method uses modified design approach by replacing the conventional multiplier by Vedic multiplier internally in the implementations. The proposed method is efficient in terms of computational speed, hardware resources and area significantly. The efficiency of the proposed algorithm is tested by simulations and comparisons with different design approaches. The proposed circuit is also modular, expandable and regular which provides flexibility

Rashmi Lomte [6] describes a methof of two finite length sequences (NXM), is implemented using direct method to reduce deconvolution processing time. The perfomance of the circuit has a delay of 79.595 ns from input to output using 90nm process. The outcome of research is high speed deconvolver implementation is achieved. Since  $4\times4$  bit multiplier is need of this project, different  $4\times4$  bit multipliers studied and Urdhava Triyakbhyam algorithm which gives lowest delay among remaining all multipliers is used .

[Jain, 2(6): June, 2015]

# International Journal OF Engineering Sciences & Management Research

#### PROPOSED WORK

Convolution is an important mathematical tool in both fields of signal and image processing. It is employed in filtering, denoising, edge detection, correlation, compression, deconvolution, simulation, and in many other applications Deconvolution is a computationally intensive digital signal processing (DSP) function widely used in applications such as imaging, wireless communication, and seismology.

The linear convolution is a basic operation in DSP which relates input signal and impulse response to obtain desired output. Consider two finite length sequences f(n) and g(n) on which the convolution operation is to be performed with lengths 1 and m respectively, the output of convolution operation y(n) contains l+m-1 number of samples. The formula for calculating discrete linear convolution is,

$$y(n) = \sum_{k=-\infty}^{\infty} x(k)h(n-k)$$

The concept of deconvolution is also widely used in the techniques of signal processing and image processing. In general, the object of deconvolution is to find the solution of a convolution equation of the form:

$$f *g = h$$

Usually, h is some recorded signal, and f is some signalthat wish to recover, but has been convolved with someother signal gbefore get recorded. The function g mightrepresent the transfer function of an instrument or a driving force that was applied to a physical system. If one know g or at least form of g, then one can perform deterministic deconvolution. Convolution is the mathematical process that relates the output, y(t), of a linear, time-invariant system to its input, x(t), and impulse response, h(t). The overlap-add method (OLA) is an efficient way to evaluate the discrete convolution between a very long signal x[n] with a finite impulse response. h[n]. The Fig.1 shows the concept of overlap add method by Zero-pad length-L blocks by M-1 samples. Add successive blocks, overlapped by M-1 samples, so that the tails sum to produce the complete linear convolution. The Block Diagram of proposed sysyetm is,

#### **CONCLUSION**

The main focus of this paper is to introduce a method for calculating the linear convolution, circular convolution and deconvolution with the help of vedic algorithms that is easy to learn and perform. An extension of the proposed linear convolution approach to circular convolution using vedic multiplier is also introduced which has less delay and area than the conventional [Jain, 2(6): June, 2015]

ISSN 2349-6193

Impact Factor (PIF): 2.243

# International Journal OF Engineering Sciences & Management Research

method. This paper also introduced a straightforward approach to performing the deconvolution. The Vedic Methods enable the practitioner improve mental abilities to solve difficult problems with high speed and accuracy. Radix-4 Booth Multiplier is giving higher speed as compared to Radix-2 Booth Multiplier and Circuit Complexity is also less as compared to it.

### **ACKNOWLEDGEMENTS**

We are very grateful to our college of HVPM College of Engineering and Technology to support and other faculty and associates of ENTC department who are directly & indirectly helped me for these paper.

### REFERENCES

- 1. Surabhi Jain & Sandeep Saini "High Speed Convolution and Deconvolution Algorithm (Based on Ancient Indian Vedic Mathematics)" IEEE transaction on education ,ECTI-Conference, May 2014.

- 2. G.Ramanjaneya Reddy, A. Srinivasulu "An Efficient Method for Implementation of Convolution" International Archive of Applied Sciences and Technology IAAST; Vol 4 [2] June 2013.

- 3. Sukhmeet Kaur, Suman and Manpreet Signh Manna, "Implementation of Modified Booth Algorithm (Radix 4) and its Comparison with Booth Algorithm (Radix-2)" Advanced in Electronic & Electric Engineering Vol 3, No.6, 2013.

- 4. Madhura Tilak "An Area Efficient, High Speed Novel VHDL Implementation of Linear Convolution of Two Finite Length Sequences Using Vedic Mathematics", IJITEE Volume-2, Issue-1, December 2012.

- 5. Asmita Haveliya "FPGA Implementation of a Vedic Convolution Algorithm", International Journal of Engineering Research and Applications (IJERA) Vol. 2, Issue 1, Jan-Feb 2012.

- 6. Rashmi Lomte and Bhaskar P.C., "High Speed Convolution and Deconvolution using Urdhva Triyagbhyam",2011 IEEE Computer Society Annual Symposium on VLSI, p.323, July 2011

- 7. Very High Speed Integrated Circuit Hardware Description Language. URL: http://electrosofts.com/vhdl/.

- 8. Honey Durga Tiwari, Ganzorig Gankhuyag, Chan Mo Kim, Yong Beom Cho "Multiplier design based on ancient Indian Vedic Mathematics" IEEE, SOC Design conference, Volume-2, NOV-2008

- 9. John W. Pierre, "A Novel Method for Calculating the Convolution Sum of Two Finite Length Sequences", IEEE transaction on education, VOL.39, NO. 1, 1996.

- 10. J. G. Proakis and D. G. Manolakis, "Digital Signal Processing: Principles Algorithm, and Applications," 2nd Edition. NewYork Macmillan, 1992

- 11. Hsin-Lei Lin, Robert C. Chang, Ming-Tsai Chan (2004), Design of a Novel Radix-4 Booth Multiplier, IEEE Asia-Pacific Conference on Circuits and Systems, Vol.2, pp. 837-840.

- 12. H. Lee, "A High-Speed Booth Multiplier", ICCS, (2002).